トランジスタギターアンプの出力段はどうなってるの?

トランジスタのギターアンプの出力段はどうなっているんでしょう?

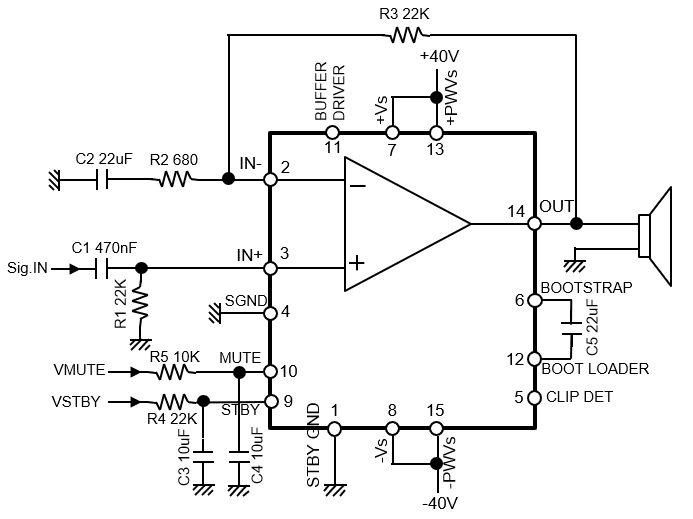

最近は出力段にICを使っているものが多いようです。まず、出力段用ICの一例としてマーシャルのトランジスタアンプMG100DFX、AVT150で使われているSTマイクロエレクトロニクス社製TDA7293に付いて説明します。次に実際にギターアンプで使われているTDA7293の周辺回路について簡単に触れます。最後に、大きな出力を持つICの特徴のひとつであるブートストラップについて説明します。

TDA7293の仕様書はSTマイクロエレクトロにクス社のホームページで入手できます。仕様書からの無断転載は出来ないことになっていますので、仕様書をダウンロードして本ページと併せてご覧ください。また実際に使う方はこちらの仕様書に記載された内容を見ていただけるようお願いいたします。仕様書の入手先は下に記載します。

www.st.com/ja/audio-ics/tda7293.html

TDA7293ってどんなIC?

まず仕様書から特徴を抜粋しました。

・BCD(バイポーラ・CMOS・DMOSの三種類をひとつのチップ上に集積する)プロセステクノロジー

・高出力電力(100W 8Ω @ THD=10% Vs=±40V)

・ミュートとスタンバイの機能

・出力短絡保護

・サーマルシャットダウン(内部が高温になるとシャットダウンする機能)

ブロックダイアグラムは仕様書のFigure 1.に載っています。ただ初心者の方には分かりずらいと思い図1に作り直してみましたので見比べてみてください。本ICは保護回路などが付いた大きなオペアンプだとみてもらえれば良いと思います。

なお、ギターアンプに限らずトランジスタのアンプといえばオペアンプの理解が必須となります。オペアンプの動作に付いてはネット上に親切な方の説明が沢山ありますのでそちらをご覧ください。もし「動作がしっくりこない」という方は、イマジナリーショートに付いて調べてみてください。きっと回路図を見ただけでその動作がイメージ出来るようになります。

図1 ブロックダイヤグラム

図1(仕様書Figure 1)の周辺部品について説明します。実際のところ設計者でなければ正確には分からないのですが推測して書いてみます。まず、オペアンプはその接続から非反転アンプ回路であることが分かります。ゲインは22K/680Ω=32.4倍=30.2dBになります。この値はTable 4のGv(Typ.)にほぼ等しいことからも、本ICは30dBに設定して使うように最適化されていると思われます。ゲインの最小値Gvmin>26dBの記載があることに注意してください。ゲインを小さくすると帯域幅は伸びますが位相余裕が減少します。22Kと660Ωに付いては仕様書の推奨値(Application suggestions)と同じ値になっています。 R3を22Kにしているのは、入力オフセット電流(Table 4のIos)X22Kを入力オフセット電圧10mV(Table 4のVos)より小さくするためです。もう一つの理由は、Noise(熱雑音=√(4kTR⊿f)=2.7uV)を内部のトータルノイズTyp3uV(Tabel 4のeN)より小さくするためです。 660Ωは22Kを1/Gainした値です。C2は入力オフセット電圧がゲイン倍されることを防ぐ目的で入れられています。+側端子は22KΩの抵抗でバイアスされ、カップリングコンデンサC1を通して信号が入力されます。R1の22Kは入力電流(Table 4のIb)によるオフセットをキャンセルさせるために帰還抵抗R3の値と合わせています。入力インピーダンスは22Kとなり問題ない値になりました。先のC2の値は、C1とR1によるハイパスフィルターのカットオフ周波数と同等以下になるように選ばれていると思われます。

MUTE端子とSTBY端子に付けられたコンデンサと抵抗は時間差を付けるためにそれぞれ異なる値となっています。MUTEの立ち上がりと立下りが共にSTBYの内側に入るようにするには仕様書のFigure 6の外付けが推奨されています。

電源端子は+側に+Vs端子と+PWVs端子を、-側は-Vs端子と-PWVs端子を用います。大きさの異なる二つのコンデンサが使われている(図1では略)のは、大きなコンデンサ(例えば電解コンデンサ)は周波数特性があまりよくないためです。小さな値のコンデンサ(例えばセラミックコンデンサ)を並列に入れて周波数特性を改善します。回路図上のGND記号は±電源の中間値である0Vを指します。ちなみに電源の±40Vは私が書き入れました。

出力の大きさを計算してみましょう。出力の振幅は最大で+側が40V、-側が-40Vです。この大きさの正弦波を80Vpp(80ボルト ピーク トゥ ピーク)といいます。電力は実効値で計算しますので 80Vpp /2 / √2になります。また、電力は電圧 X 電流 = 電圧 X (電圧 / 抵抗値)ですから

(80/2/√2) X ( (80/2/√2) / 8Ω ) = 100W になります。つまり8Ωのスピーカーで100Wを出すには少なくとも±40Vの電源が必要であることが分かります。ただし、100W出力時の歪率は比較的大きな値の10%である事に注意願います(Figure 15を参照願います)。

6Pin:12Pin間にはブートストラップ用のコンデンサが接続されています。ブートストラップに付いては後半で説明します。

実際のアンプで使われている回路は?

実際のAVT150で使われている回路は著作権の件もあり、ここには載せていません。少しだけ文章で書かせてもらいます。基本的な考え方は先の仕様書上にある回路と同じです。一番大きな違いは、フィードバックループ(R3が接続されている部分)に工夫がこらされていることです。例えばマーシャルアンプで特徴的なPRESENCEの調整は、真空管アンプと同様にフィードバックの特性を可変することで実現しています。ギターアンプはオーディオアンプと異なりギターの音を作り出します。ギターらしい音が出せるように出力段の回路も研究されています。それはメーカーの音作りが現れている重要な部分のひとつでもあります。

ブートストラップってなに?

終わりにブートストラップに付いて説明しておきます。

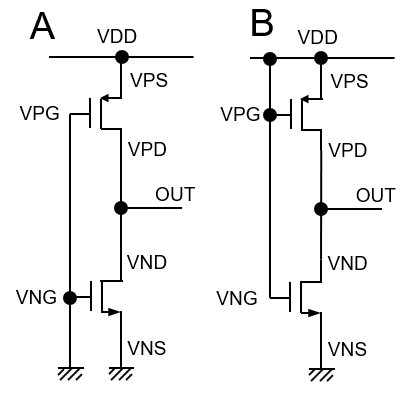

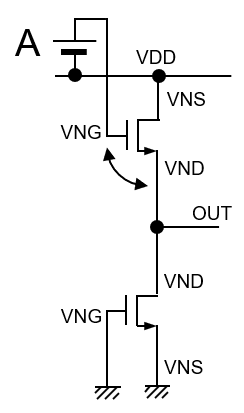

ブートストラップがなぜ必要か、その意味を含めて説明します。図2は出力段の構成について簡単に説明したものです。

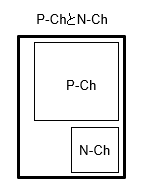

図2-1は上側にP-Ch(P-チャンネルDMOSトランジスタ)を下側にN-Ch(N-チャンネルDMOSトランジスタ)を用いたものです。図2-1のAではそれぞれのゲート電圧VPGとVNGが下がりP-ChはONに、N-ChはOFFになり、結果 出力電圧OUTは上昇します。一方図2-1のBではAとは逆に出力が下降する状態を示しました。これらの図は簡易的に表したもので、入力が最大電圧と最小電圧の間を変化する過程では出力はアナログ的に遷移することとします。ところで、P-ChとN-Chの能力を合わせようとすると、移動度の違いからP-Chの大きさはN-Chの大きさの2~3倍にする必要があります。この時のチップの様子を図3-1に示しました。少し空いている部分は、そのほかの回路部分を示します。もし、上側のDMOSトランジスタもN-Chを使えたなら図3-2の様にチップサイズを小さく、リーズナブルな値段でユーザーに提供出来るようになります。また、この差はチップの中で出力トランジスタの面積の占める割合が大きくなるほど顕著になることが想像できると思います。

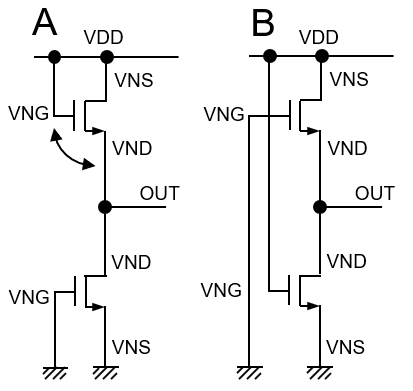

では戻って図2ー2をご覧ください。上下ともN-Chを使った場合の接続図です。Aは出力を上昇させる場合の、Bは出力を下降させる場合の接続を示しました。ここで図2-2のAに着目してみましょう。上側のN-ChをONさせ出力電圧をあげていますが、上側のN-Chのゲート:ソース間電圧が残ります。つまり出力は電源電圧(VDD)まで上げることが出来ません。この分だけ出力電力を失うことになります。そこで考えられたのが、図2ー3の様に出力を上昇させるとき、上側のN-Chのゲート電圧を電源以上に押し上げてしまおうとするものです。この仕組みをブートストラップといい、コンデンサを用いて実現しています。

ブートストラップと出力段構成

図2-1

図2ー2

図2-3

出力段構成とチップイメージ

図3ー1

図3ー2

それではブートストラップの回路例を見てみましょう。

ほぼ同等のICであるTDA7294の仕様書に分かりやすい図がありましたので、こちらを参考にして説明させてもらいます。下の場所から仕様書を入手してください。

www.st.com/content/st_com/ja/products/audio-ics/audio-amplifiers/class-ab-audio-power-amplifiers/tda7294.html

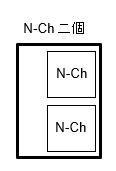

仕様書のFigure 3. Block diagramを参照願います。詳細はこちらの図を見ていただくとして、説明のためINPUT STAGEとSHORT CIRCUIT PROTECTION、それに位相補正用コンデンサを除いた回路を図4のBに載せました。図4のAはさらにブートストラップの回路を除いたものです。図4のAは出力段の動作と電流設定について説明したものです。内部のオペアンプの+端子:-端子間電圧はイマジナリーショートにより0Vとなります。結果Vgs1=Vgs2となります。M1はゲートとドレインがショートされた状態で定電流源により一定の電流Ids1が流れています。説明のためにこのIds1を100uAとします。M2のゲート:ソース間電圧はM1と等しいため、M2のサイズが同じ場合はドレイン電流Ids2はM1と同じ値になります。もしM2のサイズがM1の100倍であれば、M2のドレイン電流Ids2は10mAとなります。IN電圧が上昇するとIds2を10mAに保ったままM3のドレイン電圧Vd3(=出力電圧OUT)が下降します。逆にIN電圧が下降すればIds2を10mAに保ったままVd3(=出力電圧OUT)は上昇します。これはAB級で動作することを表しています。

図4 ブートストラップ回路例

図4のBはブートストラップを説明するためのものです。外付け抵抗により帰還(この回路中にはありません。図1ではR3で示されます)が構成されると出力電圧OUTは無信号時に0Vに設定されます。この時、コンデンサの上側のBOOTSTRAP端子電圧はツェナーダイオード電圧からNPNトランジスタのベース:エミッタ間電圧(=ダイオードの順方向電圧0.7V)を引いた値19.3Vになります。ツェナーダイオードの電圧は仮に20Vとしました。IN電圧が下降すると、出力電圧VOUTは電源電圧40V-19.3V=20.7Vまで上昇を続けます。この時コンデンサの上端BOOTSTRAP端子は電源電圧と同じ40Vになっています。さらにIN電圧が下降し出力VOUTが上昇すると、コンデンサの両端の電圧は維持されるためBOOTSTRAP端子は電源電圧を超え、電源の代わりとして動作を始めます。電流源Ⅰ1も動作を続け、M2のゲート電圧も上昇を続けます。結果出力VOUTが40Vまで上昇します。NPNトランジスタのエミッタはベースよりも高い電圧になりますが、ダイオードでいうところの逆接続(Nの電圧がPの電圧よりも高くなる)になりトランジスタには電流は流れません。電流源I1は変わらず100uAが流れAB級動作が維持されます。この電流はブートストラップ用として外付けされたコンデンサから供給されるため、コンデンサの容量をある程度大きくしておく必要があります。ブートストラップはこのようにし動作し、N-Ch DMOSでも出力電圧を電源電圧まで出すことを可能にしています。なお、20Vのツェナーンダイオードを使っているのは、定格の60Vを超えないようにするためです。

以上、出力段のICの動作について説明しました。如何でしたでしょうか。

注意事項:本投稿に記載した内容は当方の見解でありマーシャル社及びSTマイクロエレクトロニクス社から派生したもの、関連付けられたもの、または承認されたものではありません。 従ってマーシャル社及びSTマイクロエレクトロニクス社が本内容について保証するものではありません。また、本内容についてマーシャル社及びSTマイクロエレクトロニクス社に質問することはできません。

Note: The content of this post is my view only and is not derived from, associated with or endorsed by Marshall or STMicroelectronics. Therefore, Marshall and STMicroelectronics do not guarantee this content. In addition, you cannot ask Marshall or STMicroelectronics about this content.